# 2:1 MIPI CSI-2 Image Sensor Aggregator Bridge Demo

**User Guide**

UG117 Version 1.0

May 2016

### Contents

| Acronyms in This Document                                          | 3  |

|--------------------------------------------------------------------|----|

| 1. Introduction                                                    | 4  |

| 2. Functional Description                                          | 5  |

| 3. Equipment Requirements                                          | 6  |

| 4. Hardware Setup                                                  | 8  |

| 5. Device Configuration                                            | 10 |

|                                                                    |    |

| <ul><li>5.1. Programming Steps</li><li>6. Software Setup</li></ul> | 13 |

| 7. Ordering Information                                            | 14 |

| Supplemental Information                                           | 15 |

| Technical Support Assistance                                       | 15 |

| Appendix A. Debug                                                  | 16 |

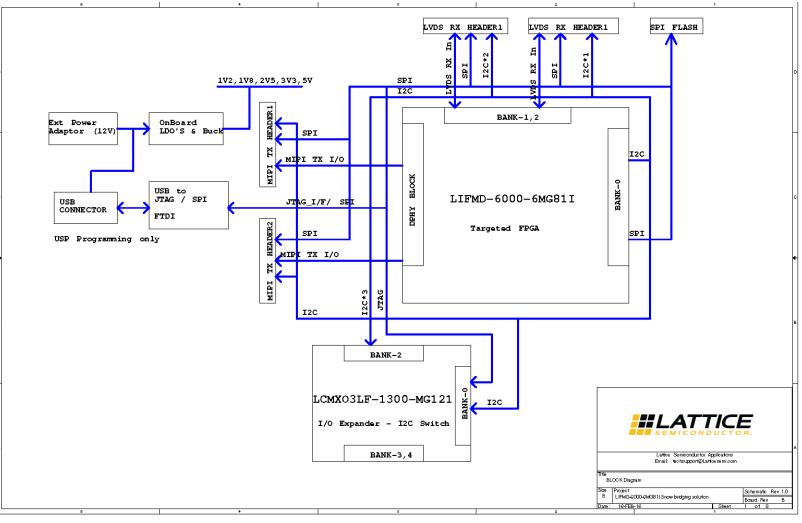

| Appendix B. LIF-MD6000 Master Link Board Schematics                | 17 |

| Appendix C. Raspberry Pi Camera Link Board                         | 25 |

| Appendix D. Raspberry Pi AP Link Board                             | 26 |

| Revision History                                                   |    |

### Figures

| igure 1.1. 2:1 MIPI CSI-2 Aggregator Bridge System Diagram               | 4 |

|--------------------------------------------------------------------------|---|

| igure 3.1. CrossLink LIF-MD6000 Master Link Board                        | 6 |

| igure 3.2. Raspberry Pi AP Link Board and Raspberry Pi Camera Link Board |   |

| igure 4.1. Rework of Raspberry Pi cameras                                | 8 |

| -igure 4.2. Assembled Demo System                                        | 9 |

| -<br>Figure 5.1. Diamond Programmer – Getting Started10                  | 0 |

| Figure 5.2. Diamond Programmer1                                          | 1 |

| Figure 5.3. LIF-MD6000 Device Properties1                                | 1 |

| Figure 6.1. Full Setup showing the Final Output of Demo                  | 3 |

| igure B.1. Block Diagram1                                                | 7 |

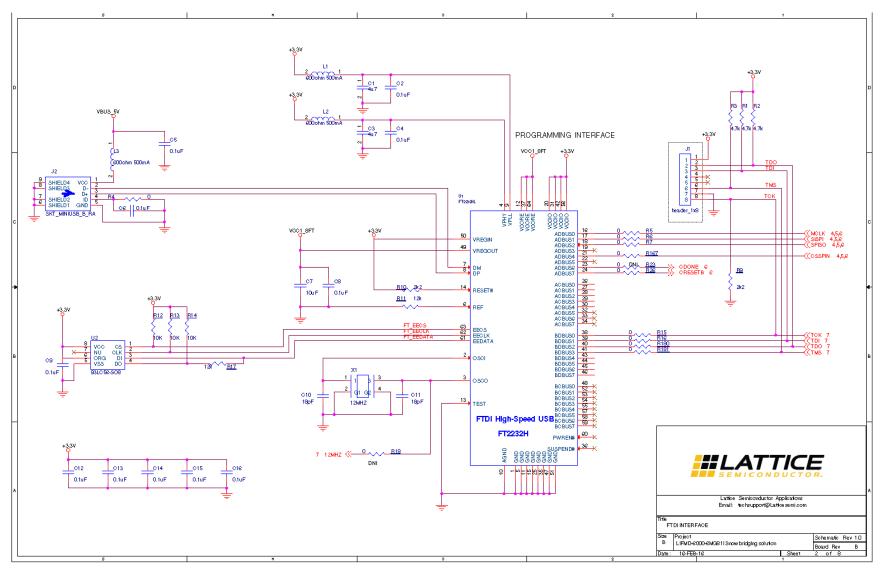

| igure B.2. FTDI Interface                                                | 8 |

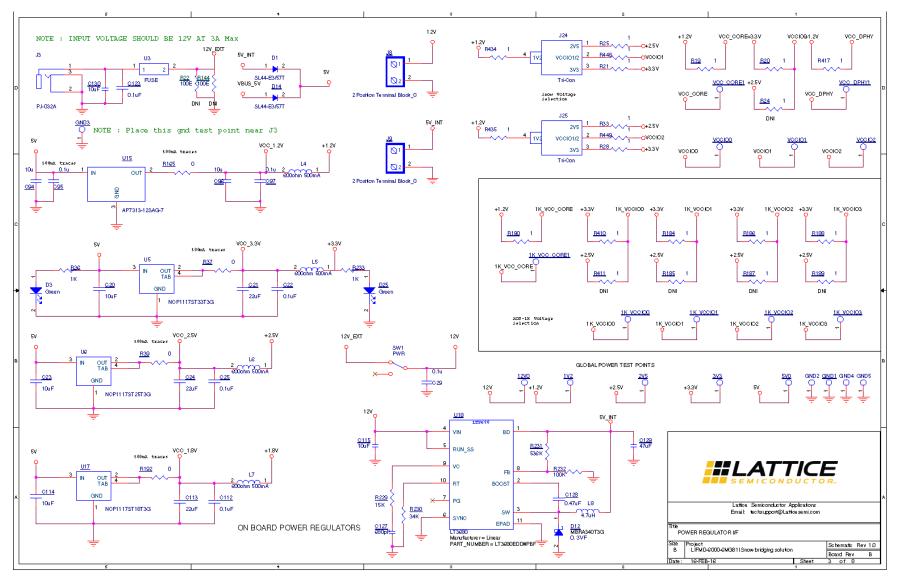

| Figure B.3. Power Regulator IF                                           | 9 |

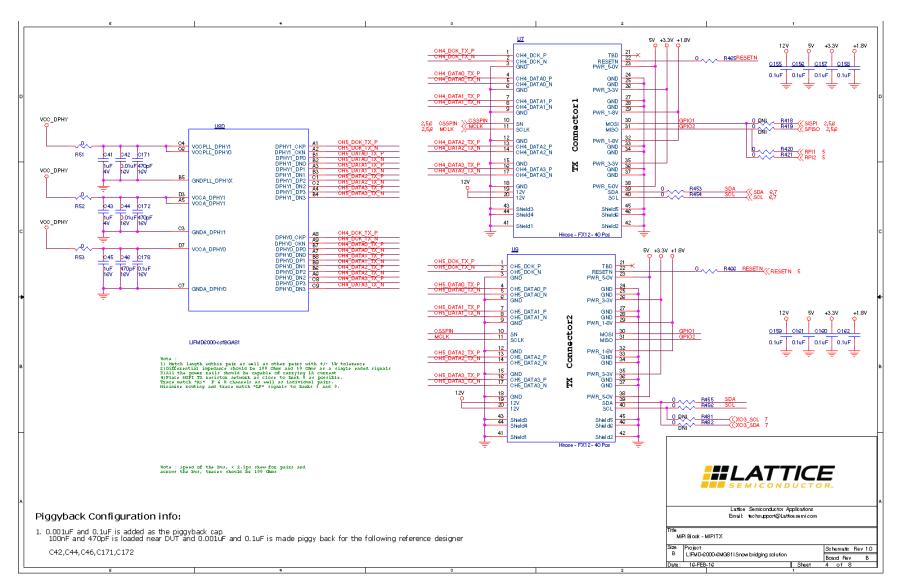

| Figure B.4. MIPI Block – MIPI TX                                         | 0 |

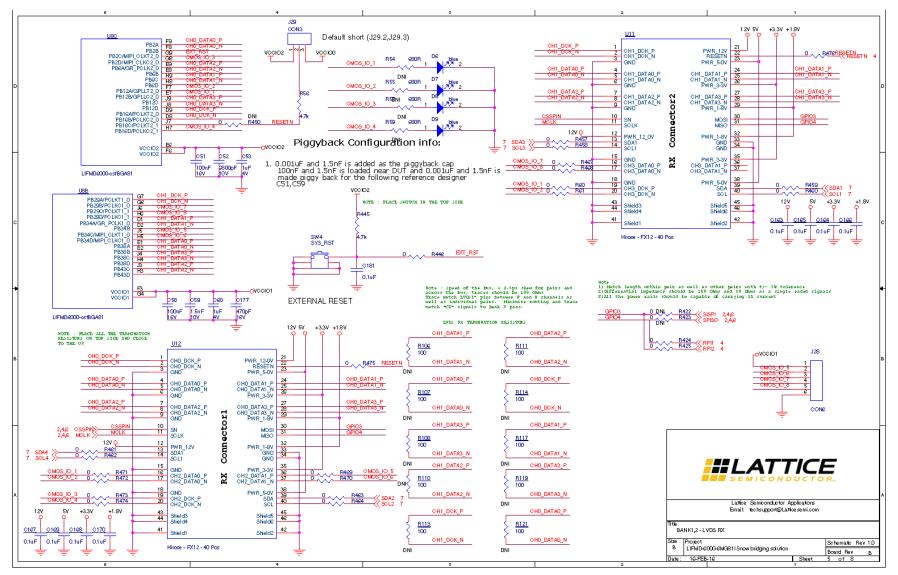

| igure B.5.Bank 1, 2 – LVDS RX                                            | 1 |

| Figure B.6. Bank0 – Flash IF                                             | 2 |

| -igure B.7. I <sup>2</sup> C Expander                                    |   |

| igure B.8. Layout Guidelines                                             |   |

| -igure C.1. Raspberry Pi Camera Link Board2                              |   |

| igure D.1. Raspberry Pi AP Link Board20                                  | 6 |

### Acronyms in This Document

A list of acronyms used in this document.

| Acronym                                      | Definition            |  |

|----------------------------------------------|-----------------------|--|

| AP                                           | Application Processor |  |

| CSI Camera Serial Interface                  |                       |  |

| DSI Display Serial Interface                 |                       |  |

| FTDI Future Technology Devices International |                       |  |

| HDMI High Definition Multimedia Interface    |                       |  |

| I <sup>2</sup> C Inter-Integrated Circuit    |                       |  |

| LVDS Low-Voltage Differential Signaling      |                       |  |

| SPI Serial Peripheral Interface              |                       |  |

| USB                                          | Universal Serial Bus  |  |

### 1. Introduction

This document describes the design and setup procedure for the Lattice Semiconductor 2:1 MIPI<sup>®</sup> CSI-2 Image Sensor Aggregator Bridge development kit to demonstrate the capabilities of the CrossLink<sup>TM</sup> FPGA in video applications.

CrossLink 2:1 MIPI CSI-2 aggregator bridge development kit is a set of boards that receives MIPI CSI-2 serial data from two image sensors, combines the image from two cameras and then transmits the combined image data to Application Processor (AP) in MIPI CSI-2 format.

The CrossLink device can receive MIPI DSI/CSI-2 data at the rate of 1.2 Gb/s/lane and transmit it at a rate of 1.5 Gb/s/lane. The device comes with full validated Soft IPs with flexible controlling options. 2:1 MIPI CSI-2 Aggregator Bridge Soft IP is used in this demonstration.

The development kit consists of three boards:

- CrossLink Master Link board featuring a Lattice LIF-MD6000 device.

- Raspberry Pi Camera Link board to connect the Raspberry Pi camera.

- Raspberry Pi AP Link board to connect to Raspberry Pi Model B+ board.

Other boards required for the demo apart from the development kit:

- Two Raspberry Pi Cameras.

- Raspberry Pi Model B+ board to process the MIPI CSI-2 data and display on an HDMI monitor.

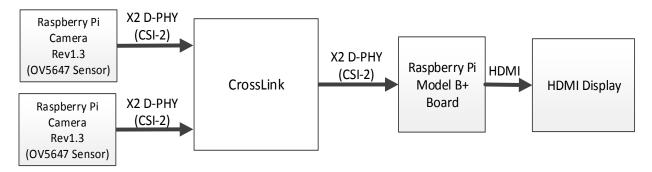

Figure 1.1 shows the 2:1 MIPI CSI-2 aggregator bridge system diagram.

Figure 1.1. 2:1 MIPI CSI-2 Aggregator Bridge System Diagram

### 2. Functional Description

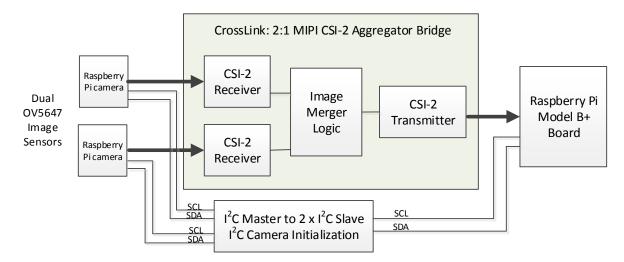

Figure 2.1 shows the 2:1 MIPI CSI-2 Aggregator IP internal block diagram. The 2:1 MIPI CSI-2 Aggregator IP receives the serial, source-synchronous MIPI data from two MIPI CSI-2 cameras, deserializes the serial data into bytes and extracts the control signal from MIPI data packets.

The IP then uses these control signals for transmitting the deserialized data to MIPI CSI-2 Transmitter block. It takes the data from both the cameras and then combines the parallel data from two data streams and then sends to MIPI CSI-2 Transmitter block. The MIPI CSI-2 Transmitter block includes Hard D-PHY block that serializes the data and sends it out in MIPI format.

Figure 2.1. Internal Block Diagram of 2:1 MIPI CSI-2 Aggregator Bridge Demo

A single I<sup>2</sup>C master to dual I<sup>2</sup>C Slave Bridge is used to configure the two Raspberry Pi cameras. The Raspberry Pi Model B+ board is configured as I<sup>2</sup>C master and the two Raspberry Pi cameras as slaves. As the Raspberry Pi AP source code is closed, we have implemented special functionalities to configure the cameras, so that the demo works in such environment. As part of this special functionality, every I<sup>2</sup>C command from Raspberry Pi Model B+ board goes to both cameras.

The  $I^2C$  Initialization block is implemented in MachXO3L device. In the MachXO3L design, the write commands are sent to both cameras simultaneously whereas, the read commands are answered by only one of these cameras. The  $I^2C$  initialization is implemented in the bridge in order to change the register settings in the Raspberry Pi camera thus enabling continuous clock mode.

### 3. Equipment Requirements

The following equipment's are required for MIPI Dual CSI-2 to CSI-2 demo:

- CrossLink Raspberry Pi 2:1 MIPI CSI-2 Aggregator Demo Kit

- CrossLink LIF-MD6000 Master Link board

- Raspberry Pi Camera Link board (2)

- Raspberry Pi AP link board

- Raspberry Pi 3 Model B V1.2 board or Raspberry Pi Model B+ board.

- Extra FPC cables used for RPi cameras

- Raspberry Pi cameras with FPC cables (2)

- HDMI monitor

- HDMI to HDMI cable

- Lattice Diamond<sup>®</sup> Programmer version 3.7 or later

- USB 2.0 Type A to Mini-B cable, included in demo kit

- USB 2.0 Type A to Micro-B cable

- Power adaptors (2), included in demo kit

- Laptop

- JED File for MachXO3L

- BIT File for CrossLink

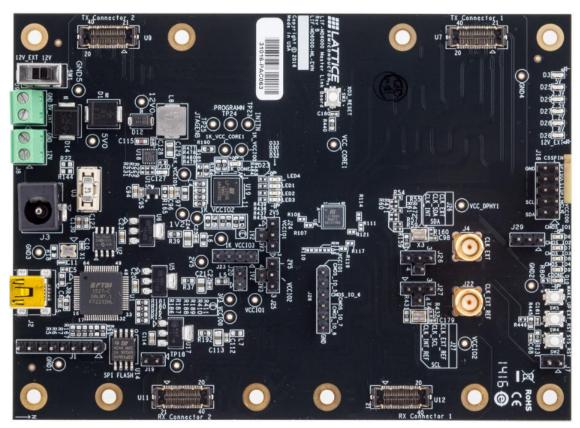

Figure 3.1 and Figure 3.2 show the top view of the CrossLink LIF-MD6000 Master Link boards used in this demo. For more details about these boards refer to <u>www.latticesemi.com/masterlink</u>.

Figure 3.1. CrossLink LIF-MD6000 Master Link Board

Figure 3.2. Raspberry Pi AP Link Board and Raspberry Pi Camera Link Board

#### **Hardware Setup** 4.

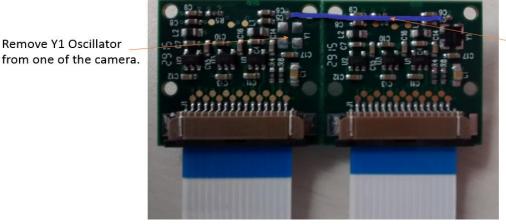

Remove Y1 Oscillator

Follow these steps to set up the hardware for 2:1 MIPI CSI-2 aggregator demo:

- 1. Take the Raspberry Pi camera 1 and remove Y1 (oscillator) on it.

- To synchronize both cameras to a single oscillator take the Raspberry Pi camera 2 and connect the test point beside 2. the oscillator of camera 2 to the same test point on Raspberry Pi camera 1. Usually in a system with two cameras, only one oscillator is used. In the most cost effective system the same clock is fed to two cameras. Fix both the cameras so that they should not move as shown below.

Connect two oscillator test points.

Figure 4.1. Rework of Raspberry Pi cameras.

- Connect U1 connector of the two Raspberry Pi Camera Link Boards to Rx connector1 and Rx connector2 of 3. CrossLink Master Link board respectively.

- Connect U1 connector of Raspberry Pi AP Link Board to TX connector1 of LIF-MD6000 Master Link board. 4.

- Fix all the boards tightly with bolts and spacers as shown in Figure 4.2. 5.

- Populate Jumpers J20, J19 and J17. 6.

- Also connect jumpers between pin2 and pin4 on both J24 and J25. 7.

- Connect the Raspberry Pi cameras with the FPC cables to J1 connector on the two Raspberry Pi Camera Link 8. boards.

- 9. Connect one end of the extra FPC cable to J1 of AP Link Board and the other end to J3 camera connector on the Raspberry Pi Model B+ board.

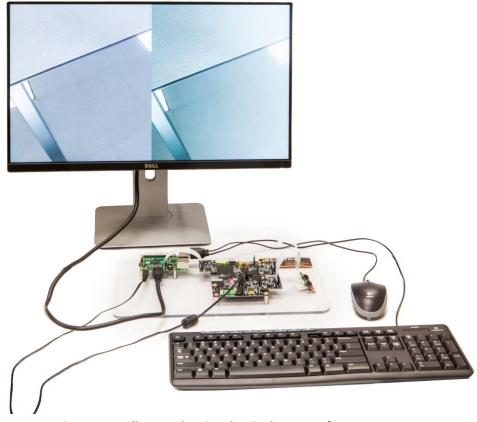

- 10. Connect the HDMI port of the Raspberry Pi Model B+ board to a screen via HDMI cable as per Figure 4.2.

Figure 4.2. Assembled Demo System

### 5. Device Configuration

This section explains the programming and configuration settings of the 2:1 MIPI CSI-2 aggregator demo kit.

The 2:1 MIPI CSI-2 Aggregator demo kit supports the programming of FPGA devices from flash device or directly through FTDI chip using Mini USB (J2) connector. The programming mode and device selection is done in Lattice Diamond Programmer. All design files required for running this demo are available on Lattice website.

The "Bitstream" folder includes the bit file and JED file required for programming the CrossLink LIF-MD6000 device and Lattice MachXO3L device, respectively.

### 5.1. Programming Steps

To program the board:

- 1. Connect the Mini USB cable to LIF-MD6000 Master Link Board.

- 2. Open the Lattice Diamond Programmer tool version 3.8 or later. The window shown in Figure 5.1 appears.

- 3. Click OK.

| 🐶 Diamond Programmer - Getting Started                 | ? ×      |

|--------------------------------------------------------|----------|

| Select an Action                                       | ]        |

| Create a new project from a JTAG scan                  |          |

| Cable: HW-USBN-2B (FTD1)   Port: FTUSB-1  Detect Cable |          |

| Create a new blank project                             |          |

| Open an existing programmer project                    |          |

|                                                        | <b>.</b> |

| 0                                                      | Cancel   |

Figure 5.1. Diamond Programmer – Getting Started

4. The Diamond Programmer automatically scans the device on the board, and the window shown in Figure 5.2 appears.

<sup>© 2016</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

|        |        | Design Window H |            |              |                                                  |                        |                                                                                                                                                                                                                                                                                                                     |

|--------|--------|-----------------|------------|--------------|--------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 🖻 🖯  | 00     |                 | 2          |              |                                                  |                        |                                                                                                                                                                                                                                                                                                                     |

| Enable | Status | Device Family   | Device     | Operation    | File Name                                        |                        | Cable Settings                                                                                                                                                                                                                                                                                                      |

|        | PASS   | LIFMD           | LIF-MD6000 | Fast Program | 6/CSFBGA81_HS/DUAL_DPHY_2_DPHY_CAMERA_HS.rbt 03/ | Cable and I/O Settings | Detect Cable         Cable:       HW-US8N-28 (FTDI) •         Port:       FTUS8-0 •         Custom port:       •         Programming Speed Settings       •         Ø Use default Clock Divider       •         TCK Divider Setting (0-10x)       1         I/O Settings       •         Ø Use default I/O settings |

| C      |        |                 | Ш          |              | X                                                |                        | Use custom I/O settings                                                                                                                                                                                                                                                                                             |

Figure 5.2. Diamond Programmer

- 5. Enable only LIF-MD6000 device and change the operation to SPI Flash Programming.

- 6. Select the options for the External SPI Flash on the board as shown in Figure 5.3.

| IFMD - LIF-MD6000 - Devi    |                                  | 9               |

|-----------------------------|----------------------------------|-----------------|

| General Device Informatio   | 1                                |                 |

| Device Operation            |                                  |                 |

| Access mode:                | SPI Flash Programming            | •               |

| Operation:                  | SPI Flash Erase,P                | rogram,Verify 🔻 |

| Programming Options         |                                  |                 |

| Programming file: C:/Use    | rs/schekoti/Desktop/csi2_to_csi2 | _impl1.bit      |

| Device Options              |                                  |                 |

| Reinitialize part on progra | am error                         |                 |

|                             |                                  |                 |

| SPI Flash Options           |                                  |                 |

| Family:                     | SPI Serial Flash                 | •               |

| Vendor:                     | Micron                           | •               |

| Device:                     | SPI-M25PX16                      | •               |

| Package:                    | 8-pin VFQFPN8                    | •               |

| SPI Programming             |                                  |                 |

| Data file size (Bytes): 10  | 3493 Lo                          | ad from File    |

| Start address (Hex):        | 0x0000000                        | •               |

| End address (Hex):          | 0x00020000                       | •               |

| Erase SPI part on pro       | gramming error                   |                 |

| Secure SPI flash gold       | en pattern sectors               |                 |

|                             |                                  |                 |

|                             |                                  |                 |

Figure 5.3. LIF-MD6000 Device Properties

- 7. Give the location of the bit file of the 2\_to\_1\_MIPI\_CSI2\_Aggregator.bit, and click Load from File.

- 8. Click OK.

- 9. Click the **Programming** button. When the programing is finished, the message *Programming successful* appears in the output window.

- 10. Change the Port in Cable settings (on the right side of Programmer window) from FTUSB-0 to FTUSB-1.

- 11. On the menu bar click **Design**, and on the drop down menu select **JTAG Scan**. The MachXO3L device on the board will be scanned by the programmer.

- 12. Provide the MachXO3L JED location and program the device. When the programing is finished the message *Programming successful* appears in the output window.

The hardware setup is completed.

### 6. Software Setup

To set up the software for 2:1 MIPI CSI-2 aggregator bridge demo:

Make sure your Raspberry Pi board is updated with the firmware "Raspbian Jessie: version March 2016 or later. The latest version of the software is available at

https://www.raspberrypi.org/downloads/raspbian/

- 2. Open the raspi-config tool from the terminal using sudo raspi-config command.

- 3. Select Enable camera and press Enter.

- 4. Go to Finish and you will be prompted to reboot.

These steps need to be done only once while configuring the setup for the first time.

5. Use the following command in the terminal to run the demo:

raspivid -o video.h264 -t 10000

When you run the above command the image should be displayed. If the message *Waiting for data* appears in the terminal window then press reset button SW4 on the board.

The final images from the two cameras side by side appear as shown in Figure 6.1 below. If the images do not appear, reset the Crosslink Master Link board.

Appendix A and Appendix B describe tips to diagnose problems with the 2:1 MIPI CSI-2 aggregator bridge demo. For details about the hardware part numbers, see Appendix A. If the hardware is correct and you do not get the demo output, see Appendix B for debug.

Figure 6.1. Full Setup showing the Final Output of Demo

<sup>© 2016</sup> Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

## 7. Ordering Information

| Description                         | Ordering Part Number | Change Summary  |

|-------------------------------------|----------------------|-----------------|

| Lattice CrossLink Master Link Board | CrossLink-ML-EVN     | Initial Release |

| RPi Camera Link Board               | RPI-CL-EVN           | Initial Release |

| RPi AP Link Board                   | RPI-APL-EVN          | Initial Release |

### **Supplemental Information**

Additional resources related to the Lattice Dual CSI-2 to CSI-2 kit including updated documentation and design project are available at <u>www.latticesemi.com/rpiboards</u>

### **Technical Support Assistance**

Submit a technical support case via www.latticesemi.com/techsupport.

### **Appendix A. Debug**

Check the following:

- 1. The part number of the cameras. The camera part number for this demo is "Raspberry Pi camera Rev 1.3". You can check this part number on the top of Raspberry Pi camera.

- 2. The version of Raspbian Jessie on the Raspberry Pi, This should be version March 2016 or later.

- 3. Run the camera demo by directly connecting the Raspberry Pi camera to the Raspberry Pi Model B+ board.

- 4. The part number of the extra FPC cable. This should be AdaFruit Industries-1646 (E248682 AWM 20941).

- 5. Check if the cables from the camera to the RPi Camera Link board are connected properly.

- 6. Check if you have mounted jumpers properly.

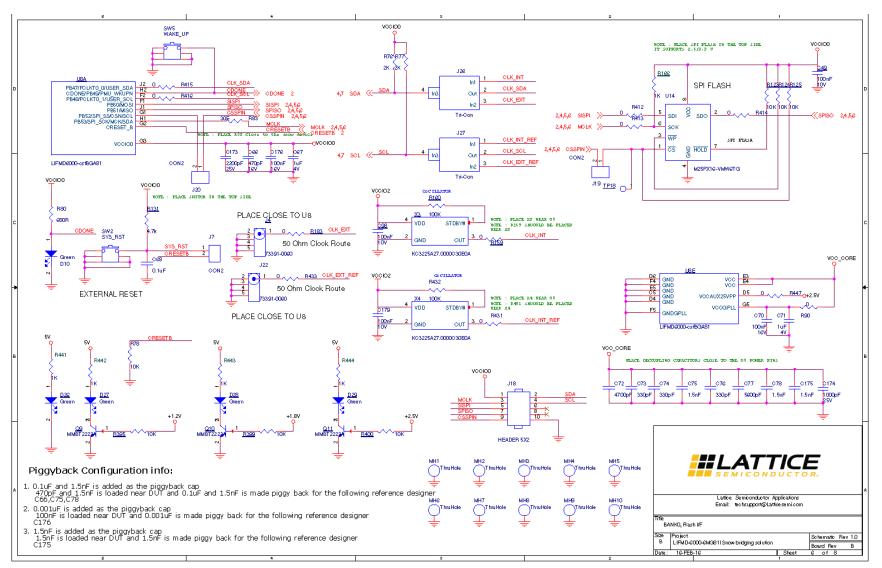

Figure B.1. Block Diagram

2:1 MIPI CSI-2 Image Sensor Aggregator Bridge Demo User Guide

Figure B.2. FTDI Interface

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

Figure B.3. Power Regulator IF

2:1 MIPI CSI-2 Image Sensor Aggregator Bridge Demo User Guide

Figure B.4. MIPI Block – MIPI TX

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

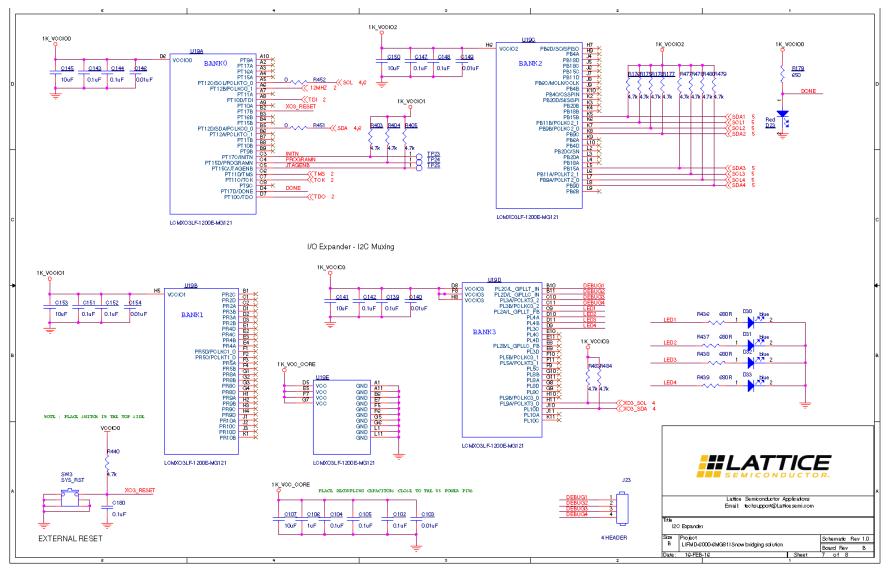

Figure B.5.Bank 1, 2 – LVDS RX

Figure B.6. Bank0 – Flash IF

Figure B.7. I<sup>2</sup>C Expander

| <br>5   4   0   2   1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Routing guidlines for MIPI & LVDS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1)All differential routes are required to have the same length between the positive (true) and the negative (complimentary) routes.<br>Spacing between the positive (true) and the negative (complimentary) shall be 2 times trace width.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2)Target differential impedance shall be 100 Ohms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3)Trace length matching to be within 1.0 mm (40 mil) across the entire bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4)Use small humps for skew corrections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5)Place signal vias close together and remove copper in between vias.<br>Traces to be fully shielded with GND stitching terminating at both trace end points                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 6)Board trace impedance results must be within ±10 percent of target and<br>Power plane impedance to be within +/- 10 percent of target at operating frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MIPI &LVDS Simulation Requirement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1)MIPI Differential Mode insertion Loss shall be > $-1.6dB$ at 750 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2)MIPI Differential Mode Return Loss shall be < $-15$ dB at 750 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3)MIPI Common Mode Return Loss shall be < -15dB at 750 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4)LVDS differential mode return loss shall be $< -16.5$ db at 600 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5)LVDS common mode return loss shall be < $-16.5$ db at 600 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6)LVDS insertion loss shall be > $-1.7$ db at 600 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7)LVDS Cross coupling shall be < -22 dB for victim IO at 600MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8)Power plane impedance to be within +/- 10 percent of target at operating frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Lattice Semiconductor Applications<br>Email: techeucoord@Latticeseni.com                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Layout Guidelines Sine Project Guidelines B Linkhot G000-GM08115row bridging solution B Linkhot G000-GM08115row bridging solution Party Provide Party ProvideParty Provide Party Provide |

| Date: 16-FEB-16 Sheet 8 of 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure B.8. Layout Guidelines

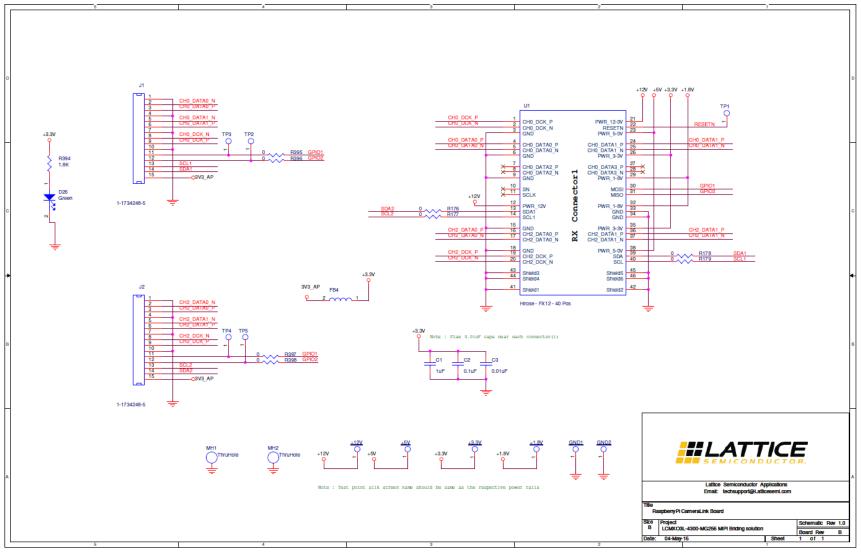

### Appendix C. Raspberry Pi Camera Link Board

Figure C.1. Raspberry Pi Camera Link Board

© 2016 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal.

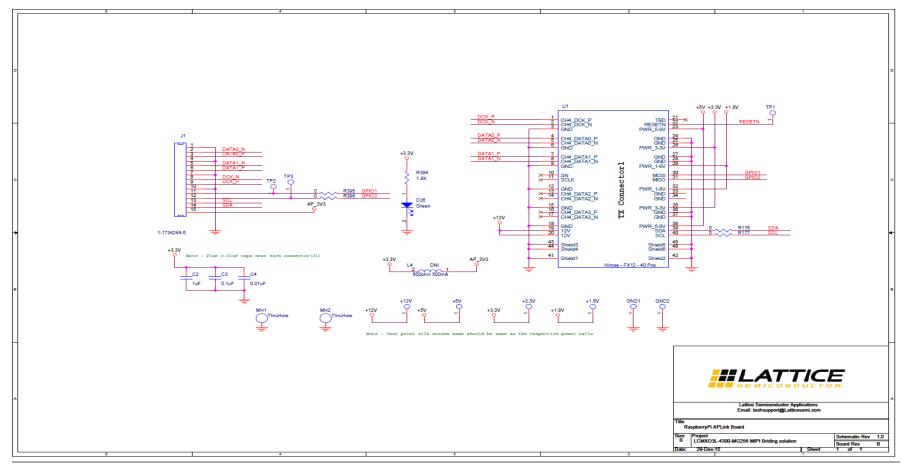

### Appendix D. Raspberry Pi AP Link Board

Figure D.1. Raspberry Pi AP Link Board

### **Revision History**

| Date     | Version | Change Summary   |

|----------|---------|------------------|

| May 2016 | 1.0     | Initial release. |

7<sup>th</sup> Floor, 111 SW 5<sup>th</sup> Avenue Portland, OR 97204, USA T 503.268.8000 <u>www.latticesemi.com</u>